本帖最后由 georgefan101 于 2013-3-21 12:17 编辑

marvell 370 cpu特性:

The Marvell® ARMADA™ 370 is a highly integrated and high-performance ARM V7-based system-on-chip (SoC) suited for a variety of home and enterprise applications. With its on-chip floating point engine, 256K L2 cache, and multiple I/O peripherals, the ARMADA 370 provides new levels of performance, integration, and efficiency, while enabling a simple system design. The ARMADA 370 is suited for a wide range of applications, including SmartHub for Home, networked attached storage (NAS) devices, media servers, and wireless access points, as well as networking and education applications.

The SoCs integrate:

• High-performance, dual-issue, and out-of-order ARMv7 CPU with Floating Point Unit (FPU) operating up

to 1.2 GHz (3000 DMIPS)

• Single/double precision FPU (VFP3-16) IEEE 754 compliant

• 32KB-instruction 4-way and 32KB-data 8-way, set-associative L1 cache

• 256KB unified 4-way, set-associative L2 cache/SRAM

• 16-bit DDR3/L-1333 memory interface

• Two Ethernet networking MACs controllers

• Four SERDES lanes with versatile muxing options for SGMII, PCIe2.0, and SATA2.0

• Two x1 PCI Express 2.0 interfaces

• Two SATA Gen2.0 ports

• Two USB 2.0 host/device ports with integrated PHY

• Network security engine with various encryption algorithm support

• Two TDM channels

• SDIO/MMC, NAND flash, two SPI, two TWSI, Device Bus, I2S/SPDIF and two UART interfaces

• Two DMA/XOR engines with two independent channels per each engine

• RTC and thermal sensor

• 286-pin HSBGA 19 x 19 mm, 1 mm ball pitch, green-compliant package

The innovative Coherency Fabric architecture provides a coherent interconnect between the CPU and the I/Os. The bus efficiency also enables a high-frequency, high-bandwidth, and low-latency access time throughout the CPU memory subsystem.

The on-chip Mbus architecture, a Marvell proprietary crossbar interconnect for non-blocking any-to-any connectivity, enables concurrent transactions among multiple units. This design results in high system throughput, enabling system designers to create high-performance products. |

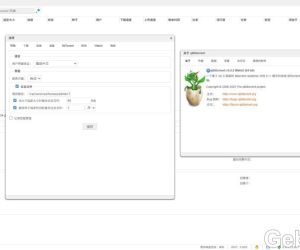

qBittorrent 套件分享1276 人气#黑群晖

qBittorrent 套件分享1276 人气#黑群晖 无效的pat1523 人气#黑群晖

无效的pat1523 人气#黑群晖 使用lucky反代群晖后 手机端photos无法备份1342 人气#黑群晖

使用lucky反代群晖后 手机端photos无法备份1342 人气#黑群晖 DSM6 套件版qbittorrent 5.0.52962 人气#黑群晖

DSM6 套件版qbittorrent 5.0.52962 人气#黑群晖